# Airgap Interconnects: Modeling, Optimization, and Benchmarking for Backplane, PCB, and Interposer Applications

Vachan Kumar, *Student Member, IEEE*, Rohit Sharma, *Member, IEEE*, Erdal Uzunlar, *Student Member, IEEE*, Li Zheng, Rizwan Bashirullah, *Member, IEEE*, Paul Kohl, *Member, IEEE*, Muhannad S. Bakir, *Senior Member, IEEE*, and Azad Naeemi, *Senior Member, IEEE*

**Abstract**—Frequency and time domain models are developed for backplane (BP), printed circuit board (PCB), and silicon interposer (SI) links using six-port transfer matrices (*ABCD* matrices) for bumps, vias and connectors, and coupled multiconductor transmission lines for traces. The six-port transfer matrix approach enables easy computation of the transfer function, as well as near-end and far-end crosstalk. The intersymbol interference is accounted for by computing the pulse response for the worst case bit pattern. Furthermore, the models developed here are used to optimize the data-rate and trace width for each of the links, so that the aggregate bandwidth obtained per joule of energy supplied to the link is maximized. The modeling and optimization approach developed here serves as a good platform to compare the air-gap interconnects against BP, PCB, and SI interconnects on lossy dielectrics. It is shown that air-gap interconnects can provide an aggregate bandwidth improvement of  $3\times$ – $4\times$  for BP links at a comparable energy per bit, and a  $5\times$ – $9\times$  improvement in aggregate bandwidth of PCB links at the expense of 20% higher energy per bit. For SI links, air-gap interconnects are shown to provide a  $2\times$ – $3\times$  improvement in aggregate bandwidth and a  $1\times$ – $1.5\times$  improvement in energy per bit.

**Index Terms**—Air-gap interconnects, chip-to-chip interconnects, data-rate and trace-width co-optimization, fine-pitch interconnects, silicon interposer (SI), time-domain modeling.

## I. INTRODUCTION

RECENT advances in gigascale integration have provided unprecedented computation power at the chip-level that must be complemented with high-bandwidth, low-power

Manuscript received November 24, 2013; revised March 17, 2014; accepted May 5, 2014. Date of publication June 17, 2014; date of current version July 31, 2014. This work was supported in part by the Global Research Collaboration and in part by the Interconnect Focus Center Programs, Semiconductor Research Corporation. Recommended for publication by Associate Editor D. G. Kam upon evaluation of reviewers' comments.

V. Kumar, L. Zheng, M. S. Bakir, and A. Naeemi are with the School of Electrical and Computer Engineering, Georgia Institute of Technology, Atlanta, GA 30332 USA (e-mail: vkumar38@gatech.edu; lizheng@gatech.edu; muhannad.bakir@mirc.gatech.edu; azad@gatech.edu).

R. Sharma is with the Department of Electrical Engineering, IIT Ropar, Rupnagar 140001, India (e-mail: rohitsharma@gatech.edu).

E. Uzunlar and P. Kohl are with the School of Chemical and Biomolecular Engineering, Georgia Institute of Technology, Atlanta, GA 30332 USA (e-mail: erderuzunlar@gatech.edu; paul.kohl@che.gatech.edu).

R. Basirullah is with the Department of Electrical and Computer Engineering, University of Florida, Gainesville, FL 32611 USA (e-mail: rizwan@ufl.edu).

Color versions of one or more of the figures in this paper are available online at <http://ieeexplore.ieee.org>.

Digital Object Identifier 10.1109/TCMT.2014.2326798

off-chip interconnects. Microprocessor input/output (I/O) bandwidth demands approximately double every two years [1], [2]. Hence, conventional chip-to-chip interconnects, which suffer from significant conductor and dielectric losses at higher frequencies, have become major bottlenecks in high performance nanoelectronic systems [3], [4]. Without considerable improvement in the performance and power of chip-to-chip interconnects, the boost in performance at the chip level cannot be translated to system-level improvements. Hence, many alternative technologies, including optical interconnects [5]–[7], 3-D-ICs [8]–[10], silicon interposers (SIs) [11]–[14], and air-gap interconnects [15]–[23], are being investigated. Optical interconnects have very little loss over long lengths, but due to the overhead of conversion to/from the electrical domain, they are mainly useful for longer interconnects at the backplane (BP) level in high performance servers and supercomputers [24]. Three dimensional (3-D) integration, on the other hand, aims to minimize the physical distance between the communicating ICs by stacking them on top of each other using through silicon vias. However, due to the challenges involved with heat removal from high performance 3-D-ICs, it is essential for researchers to push the performance and energy of planar interconnects to their limit. Among the novel planar interconnect technologies, SIs achieve significantly high aggregate bandwidth due to the use of very fine-pitch interconnects, whereas the performance and energy improvement in air-gap interconnects is mainly due to reduced dielectric losses and reduced capacitance. Hence, it is interesting to compare the two technologies against each other, and against the conventional links on FR-4 printed circuit boards (PCBs).

There have been numerous studies on air-gap interconnects, but they were mainly focused on process integration and reliability issues [15]–[23]. The fabrication of air-gap interconnects is done using polypropylene carbonate (PPC) as a sacrificial polymer, which thermally decomposes at higher temperatures to form the air gaps [25], [26]. Models for the reduction in capacitance or loss tangent of air-gap interconnects are available [15], [23]. However, the computation of capacitance and loss tangent are not sufficient to estimate the improvement achieved in a real system, including IO circuits. Additionally, multiple process and design constraints on both conventional and air-gap interconnects are essential for a fair comparison between the two technologies. For example,

conventional PCB interconnects are limited by a minimum width and spacing of 4 mils (101.6  $\mu\text{m}$ ) [27], whereas air-gap interconnects are limited to smaller widths due to their small air-gap height for mechanical reliability. These interesting tradeoffs can be captured through a comprehensive frequency and time domain modeling approach developed in this paper. The models developed here consider multiple channel components such as bumps, vias, package traces and connectors, and noise due to intersymbol interference (ISI) and crosstalk. For fast design space exploration compared with extraction and HSPICE simulations [28], the modeling approach uses analytical models for computing the transmission line parameters. Available papers on link optimization focus either on data-rate and energy per bit [29], [30], or the estimation of maximum aggregate bandwidth as a function of data-rate and number of PCB layers [31]. However, this paper focuses on the co-optimization of data-rate and trace width to maximize the aggregate bandwidth per joule of energy supplied to the link. Although the optimization methodology was developed in [32], the modeling approach has been modified significantly to include the discontinuities like vias and bumps, realistic air-gap structures, near-end crosstalk (NEXT) and far-end crosstalk (FEXT), and timing jitter. In addition, the modeling and optimization techniques are applied to SIs and the improvement offered by air-gap interconnects for BP, PCB, and SI links are discussed.

This paper is organized as follows. Section II describes the modeling approach used in this paper, including the link architectures, parasitic extraction, and modeling for different components of the link, and frequency domain and time domain modeling techniques. The optimization methodology to simultaneously maximize aggregate bandwidth and minimize energy per bit is developed in Section III. A comparison of the aggregate bandwidth and energy of air-gap interconnects against conventional interconnects on a BP, PCB, and SI is presented in Section IV. The processes and challenges associated with the fabrication of air-gap structures are discussed in Section V. Important conclusions from this paper are summarized in Section VI.

## II. MODELING APPROACH

The approach to modeling BP, PCB, and SI links is presented in this section. The different components of each link are described followed by an explanation of the extraction and compact models used for estimating their parasitics. The extracted parasitics and compact models are then converted to a transmission matrix form [33], such that the effective transmission matrix can be obtained by an ordered multiplication of the transfer matrices of the individual components. The effective transfer matrix is then combined with the boundary conditions to extract useful frequency domain information about the channel, including the frequency response, NEXT, and FEXT. Finally, the frequency domain information is used to obtain the time domain pulse response, NEXT and FEXT in the system. Based on certain noise assumptions and bit error rate (BER) requirements, the minimum current/voltage swing at the transmitter for reliable detection at the receiver is determined.

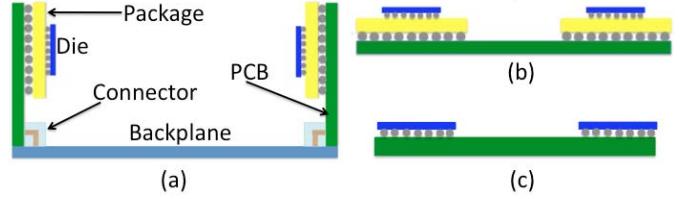

Fig. 1. Schematic view of (a) BP link, (b) PCB link, and (c) SI link.

Furthermore, the minimum current/voltage swing requirement is used to compute the power and energy per bit consumed in the transmitter. It is assumed that the current/voltage swing at the transmitter can be programmed, as demonstrated in [1].

### A. Link Architectures and Interconnect Structures

In order to estimate the performance and energy gains obtained using air-gap interconnects, three different links shown in Fig. 1 are analyzed. BP and PCB links are chosen to study the impact of air-gap interconnects on long and short links, respectively. SI is a relatively new technology using very fine-pitch interconnects with high conductor losses. Hence, it is interesting to investigate if air-gap interconnects are helpful for SI links. Based on the typical link architectures for BPs and PCBs presented in [1], the links are assumed to be driven by differential current mode driver circuits and terminated at the receiver by a matched impedance. Similarly, based on the interposer link architecture presented in [14], the link is assumed to be driven by differential voltage mode circuits with high impedance termination at the receiver.

- 1) *BP Link*: The BP link consists of microbumps, package vias and traces, C4 bumps, PCB vias and traces, BP connectors, and BP traces. The package and PCB trace lengths are assumed to be 5 mm and 10 cm, respectively, at both the transmitter and receiver ends. The length of the BP trace is varied from 20 to 50 cm.

- 2) *PCB Link*: This link consists of microbumps, package and PCB vias and traces, and C4 bumps. The package traces are assumed to be 5-mm long and the PCB trace lengths are varied from 2 to 10 cm. Since the traces are short, the reflections at the vias and solder bumps are important here.

- 3) *SI Link*: In this case, the link consists of microbumps at the transmitter and receiver dies, and fine-pitch interconnects on a silicon carrier. The trace lengths are varied from 2 to 6 cm. Since the traces are a few micrometer wide, it is argued in [34] that the reflections from the impedance mismatch at the receiver suffer a significant round trip attenuation, thus adding negligible noise to the receiver. As a result of this mismatched impedance, the differential impedance of the traces need not be constrained to 100  $\Omega$ .

### B. Extraction or Modeling of Interconnect Circuit Parameters

The approach used for the extraction and modeling of interconnect circuit parameters is described here. Initially, the link is divided into multiple physical components,

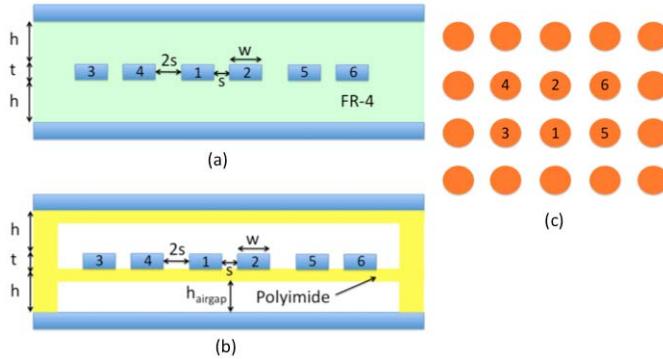

Fig. 2. Cross section of differential striplines used as the interconnect for high-speed links with (a) lossy dielectric and (b) air-gap dielectric. (c) Cross section of the package/PCB via array used for the extraction of parasitics.

e.g., the BP link could be divided into microbumps, C4 bumps, package and PCB vias, package and PCB traces, connectors, and BP traces. The two key variables used in design space exploration are data-rate and trace width. As a result, the only parasitics that depend on the design variables are those of the transmission lines used in the BP, PCB, or interposer links. The parasitics of the rest of the components do not vary with the design variables and are therefore modeled using Synopsys Raphael [35]. For this analysis, three differential pairs are considered, thus resulting in  $6 \times 6$  parasitic matrices for each of the elements. Arrays of microbumps and C4 bumps are modeled using lumped capacitance matrices using 3-D Raphael. For the microbumps, the diameter and pitch are assumed to be 25 and 50  $\mu\text{m}$ , respectively. For the C4 bumps, the diameter and pitch are assumed to be 250 and 400  $\mu\text{m}$ , respectively. The package and PCB via capacitances are extracted using 3-D Raphael; however, since the 3-D inductance extraction is not trivial, and since the focus of this analysis is on transmission lines, the via inductance is estimated using 2-D Raphael. The inductance values obtained using 2-D Raphael are of the same order as the ones derived using simple analytical equations [36]. The package vias are assumed to have a radius of 15  $\mu\text{m}$ , via-via pitch of 60  $\mu\text{m}$ , and height of 50  $\mu\text{m}$ , in accordance with the stack-up given in [37]. The PCB vias are assumed to have a radius of 300  $\mu\text{m}$ , and a pitch of 1 mm. The connector traces are treated as transmission lines of length 1 cm, radius 300  $\mu\text{m}$ , and pitch 2 mm.

The BP, PCB, and SI traces are modeled as coupled differential transmission lines, with a cross section shown in Fig. 2(a) for conventional interconnects, cross section shown in Fig. 2(b) for air-gap interconnects, and cross section shown in Fig. 2(c) for package and PCB vias. The cross-sectional dimensions chosen for the simulation of conventional and air-gap interconnects are given in Table I. Since the trace width is a key design variable, it is essential to have the capability to quickly compute the effect of varying the width on the transmission line circuit parameters. As a result, it is not a good idea to run Raphael for RLGC extraction at every design point. Instead, previously derived analytical equations from [38] and [39] are used for estimating the capacitance and frequency dependent resistance, respectively.

TABLE I

CROSS-SECTONAL DIMENSIONS USED FOR THE SIMULATION OF CONVENTIONAL AND AIR-GAP INTERCONNECTS IN MICROMETER ( $w$  IS THE WIDTH)

|              | BP/PCB + FR-4                       | BP/PCB + Airgap                     | SI + $SiO_2$ | SI + Airgap |

|--------------|-------------------------------------|-------------------------------------|--------------|-------------|

| $h$          | 304.8                               | 23.6                                | 3            | 6.6         |

| $h_{airgap}$ | -                                   | 20                                  | -            | 3           |

| $t$          | 17.8                                | 17.8                                | 3            | 3           |

| $s$          | Designed for $Z_{diff} = 100\Omega$ | Designed for $Z_{diff} = 100\Omega$ | 0.66w        | 0.66w       |

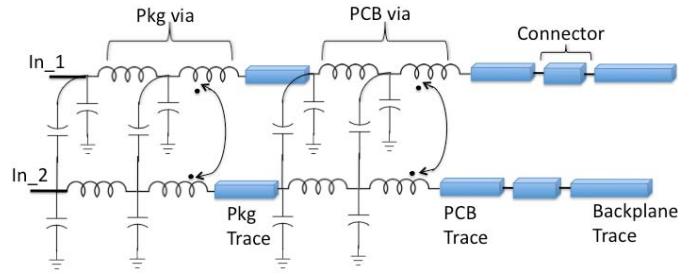

Fig. 3. Circuit model of the transmitter half of a BP channel, showing one differential pair going through pads, solder balls, package vias, package traces, PCB vias, PCB traces, connectors, and BP traces. The receiver half of the BP channel is assumed to be a mirror image of the transmitter half. The analysis includes three differential pairs, which are coupled, thus forming a six-port network for analysis.

For PCB and BP interconnects, an rms surface roughness of 0.81  $\mu\text{m}$  is assumed, in accordance with [40]. The inductance matrix  $[L]$  is computed from the capacitance matrix  $[C]$  as  $[L] = (\epsilon_r/v_0^2)[C]^{-1}$ , where  $\epsilon_r$  is the dielectric constant of the medium, and  $v_0$  is the speed of light in vacuum.

### C. Frequency Domain Modeling and Validation

The extracted parasitic matrices, and the analytically derived parameters for the different components are combined to form a circuit model for the six-port network representing each of the above links. The transmitter half of the circuit model of a BP channel is shown in Fig. 3. The figure just shows two out of the six lines that form the six-port network. The extracted matrices from the different components are then converted to  $12 \times 12$  transfer matrices (similar to  $ABCD$  matrices, but with  $6 \times 6$  matrices for each of the elements  $A$ ,  $B$ ,  $C$ , and  $D$ ). The transfer matrices for the transmission lines are derived from the Resistance Inductance Conductance Capacitance (RLGC) matrices using multiconductor transmission line (MTL) analysis, as shown in [33, Ch. 4]. To ensure causality in the time domain, conductor loss models given in [41] and frequency-dependent dielectric models given in [42] are used. Once the transfer matrices of each of the components are obtained, the effective transfer matrix is computed as the product of the transfer matrices of all the components. Mathematically, the voltage and current relation between the inputs and outputs is given by

$$\begin{bmatrix} [V_{in}]_{6 \times 1} \\ [I_{in}]_{6 \times 1} \end{bmatrix} = \begin{bmatrix} [\Phi_{11}]_{6 \times 6} & [\Phi_{12}]_{6 \times 6} \\ [\Phi_{21}]_{6 \times 6} & [\Phi_{22}]_{6 \times 6} \end{bmatrix} \begin{bmatrix} [V_{out}]_{6 \times 1} \\ [I_{out}]_{6 \times 1} \end{bmatrix}. \quad (1)$$

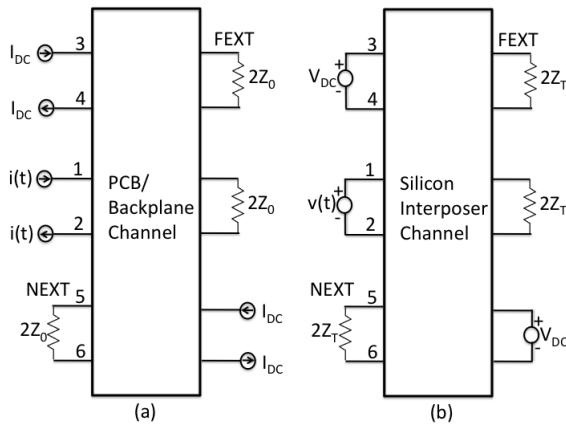

Fig. 4. Boundary conditions for (a) PCB/BP link and (b) SI link.

The boundary conditions applied to the different links are shown in Fig. 4. While the BP and PCB links are assumed to be driven by differential current mode circuits and terminated with a matched impedance (100- $\Omega$  differential impedance), the SI links are assumed to be driven by differential voltage mode circuits and terminated with a high impedance (2-k $\Omega$  differential) at the receiver. By applying these boundary conditions to (1), the differential output voltage at the receiver, NEXT, and FEXT are obtained. The differential output at the receiver is given by (2) for current mode drivers, and by (3) for voltage mode drivers

$$\frac{V_{\text{out\_diff\_12}}}{I_{\text{in1,2}}} = Z(1,1) + Z(2,2) - Z(1,2) - Z(2,1) \quad (2)$$

$$\frac{V_{\text{out\_diff\_12}}}{V_{\text{in\_diff\_12}}} = \frac{T(1,1) + T(2,2) - T(1,2) - T(2,1)}{2}. \quad (3)$$

In the equations above,  $V_{\text{out/in\_diff\_xy}} = V_{\text{out/in}}(x) - V_{\text{out/in}}(y)$ ,  $[Z]$  is the matrix relating the input current to the output differential voltage, and  $[T]$  is the voltage transfer matrix relating the input differential voltage to the output differential voltage given by (4) and (5). In the equations given below,  $2Z_T$  is the differential termination impedance, which is assumed to be 100  $\Omega$  for BP/PCB links, and 2 k $\Omega$  for SI links

$$[Z] = \left( \Phi'_{21} + \frac{\Phi'_{22}}{Z_T} + \Phi''_{21} [M_B] \right)^{-1} \quad (4)$$

$$[T] = \left( \Phi'_{11} + \frac{\Phi'_{12}}{Z_T} + \Phi''_{12} [M_C] \right)^{-1} \quad (5)$$

$$[M_A] = \left[ \Phi'''_{11} + \frac{\Phi'''_{12}}{Z_T} + Z_T \Phi'''_{21} + \Phi'''_{22} \right] \quad (6)$$

$$[M_B] = - \left( \Phi'''_{11} + Z_T \Phi'''_{21} \right)^{-1} [M_A] \quad (7)$$

$$[M_C] = - \left( \Phi'''_{12} + Z_T \Phi'''_{22} \right)^{-1} [M_A] \quad (8)$$

$$\Phi'_{xy} = \Phi_{xy}(1 : 4, 1 : 4); \quad \Phi''_{xy} = \Phi_{xy}(1 : 4, 5 : 6)$$

$$\Phi'''_{xy} = \Phi_{xy}(5 : 6, 1 : 4); \quad \Phi''''_{xy} = \Phi_{xy}(5 : 6, 5 : 6).$$

The differential FEXT, at the output ports 3 and 4 is given by (9) for current mode drivers, and by (10) for voltage mode

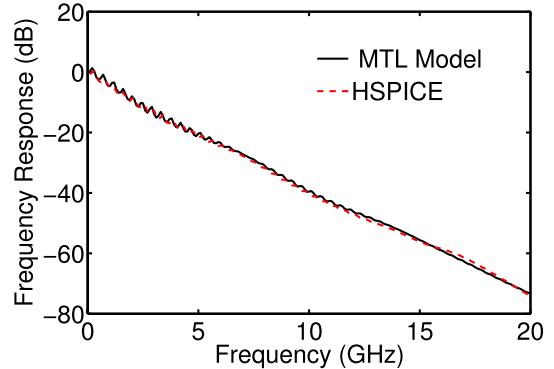

Fig. 5. Frequency response of the BP channel computed using multi-MTL models and using HSPICE.

drivers

$$\frac{V_{\text{out\_diff\_34}}}{I_{\text{in1,2}}} = Z(3,1) + Z(4,2) - Z(3,2) - Z(4,1) \quad (9)$$

$$\frac{V_{\text{out\_diff\_34}}}{V_{\text{in\_diff\_12}}} = \frac{T(3,1) + T(4,2) - T(3,2) - T(4,1)}{2}. \quad (10)$$

The differential NEXT, at the output ports 5 and 6 is given by (11) for current mode drivers, and by (12) for voltage mode drivers

$$\frac{V_{\text{out\_diff\_56}}}{I_{\text{in1,2}}} = F(1,1) + F(2,2) - F(1,2) - F(2,1) \quad (11)$$

$$\frac{V_{\text{out\_diff\_56}}}{V_{\text{in\_diff\_12}}} = \frac{G(1,1) + G(2,2) - G(1,2) - G(2,1)}{2} \quad (12)$$

where

$$[F] = \left[ \Phi'''_{11} + \frac{\Phi'''_{12}}{Z_T} + \Phi'''_{11} [M_B] \right] [Z] \quad (13)$$

$$[G] = \left[ \Phi'''_{11} + \frac{\Phi'''_{12}}{Z_T} + \Phi'''_{12} [M_C] \right] [T]. \quad (14)$$

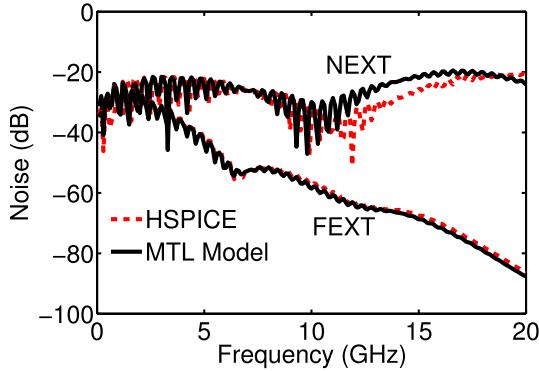

To construct the HSPICE circuit model shown in Fig. 3, the parasitics of different components, such as pads, bumps, and package and PCB vias, are extracted using Synopsys Raphael. The RLGC parameters of the transmission lines are then computed for the structure shown in Fig. 2(a) and fed into the HSPICE W-element model. The frequency response of a 50-cm BP link obtained using the MTL model and HSPICE is shown in Fig. 5, whereas the NEXT and FEXT are shown in Fig. 6. The results obtained with the MTL models match the results from HSPICE simulations, with minor differences due to the differences in the frequency-dependent circuit parameters in the MTL model and the W-element model in HSPICE.

#### D. Time Domain Modeling and Validation

The frequency domain models developed in the previous section are used to obtain the pulse response of the system. The input to the system is assumed to be a periodic pulse train with a time period  $T_P$ , a finite rise/fall time  $T_R$ , and a

Fig. 6. NEXT and FEXT in a BP channel computed using MTL models and HSPICE.

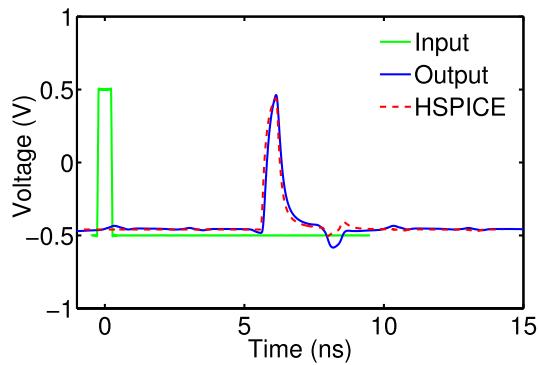

Fig. 7. Time domain pulse response of a BP link with a trace of length 50 cm, computed using six-port MTL models and HSPICE.

bit period  $T_B = 1/DR$ , where DR is the data-rate. Thus, the Fourier series of the input pulse train is given by

$$\text{in}(t) = \frac{T_B}{T_P} + \sum_{n=1}^{n=N_{\max}} a_n \cos\left(\frac{2\pi n t}{T_P}\right) \quad (15)$$

$$a_n = \frac{2T_P}{\pi^2 n^2 T_R} \sin\left(\frac{\pi n T_B}{T_P}\right) \sin\left(\frac{\pi n T_R}{T_P}\right) \quad (16)$$

where  $N_{\max}$  is the maximum number of harmonics used for building the time domain pulse. To emulate the worst case scenario for ISI (a string of 0s followed by a 1), the bit period is chosen such that  $T_P \geq 10T_B$ . The rise/fall time of the signal is assumed to be 10% of the bit period. A four-tap finite-impulse response filter at the transmitter end is assumed to equalize the low pass channel. If  $H(f)$  is the complex frequency response of the system, including the equalizer, its time domain response to the pulse (15) is given by (17). The pulse responses obtained with the model and HSPICE are shown in Fig. 7. The model developed here matches very well with HSPICE simulations

$$\text{out}(t) = \frac{T_B H(0)}{T_P} + \sum_{n=1}^{n=N_{\max}} a_n \left| H\left(\frac{n}{T_P}\right) \right| \cos\left(\frac{2\pi n t}{T_P} + \angle H\left(\frac{n}{T_P}\right)\right). \quad (17)$$

Based on the estimated time of flight and a timing jitter of 30% of the bit period, the voltage at the input of the

receiver is computed. Similarly, the worst case NEXT and FEXT voltages are also computed. In addition to crosstalk, some fixed noise sources at the receiver, such as receiver offset and receiver sensitivity, along with a noise margin to achieve a BER of  $10^{-12}$  specified in [3], are considered, resulting in an effective voltage margin of 46 mV. Depending on the quality of the receiver and BER requirements, the voltage margin can change; however, any change in the voltage margin just scales the current/voltage requirement and does not significantly affect the optimization and the conclusions. For a current mode driver, the minimum current and power required at the transmitter are given by

$$I_{\min} \geq \frac{V_{\text{margin}}}{(v_{\text{out\_diff\_12}} - v_{\text{next}} - v_{\text{fext}}) |_{I_{1,2}=1\text{Amp}}} \quad (18)$$

$$P_{\text{tot}} = E_{\text{pre}} \text{DR} + V_{\text{DD}} I_{\min} \quad (19)$$

where  $V_{\text{DD}}$  is the I/O supply voltage assumed to be 1.2 V, and  $E_{\text{pre}}$  is the energy consumed in the predriver circuits and DR is the data-rate. The main component of power consumed in the predriver circuits is assumed to be dynamic power, resulting in a constant energy per bit. To ensure a very small voltage drop across the switches, the current mode driver switches are designed for a resistance of  $5 \Omega$  and the voltage mode switches are designed for  $10 \Omega$  at the 22-nm predictive technology node [43]. This results in a predriver energy of 0.207 pJ for current mode drivers and 0.115 pJ for voltage mode drivers. For voltage mode driver circuits, the minimum voltage and power at the transmitter are given by

$$V_{\min} \geq \frac{V_{\text{margin}}}{(v_{\text{out\_diff\_12}} - v_{\text{next}} - v_{\text{fext}}) |_{V_{\text{in\_diff\_12}}=1\text{V}}} \quad (20)$$

$$P_{\text{tot}} = E_{\text{pre}} \text{DR} + \int_{t=0}^{t=4T_B} v_{\text{in\_diff\_12}}(t) i_{\text{in}_{1,2}}(t) dt. \quad (21)$$

### III. CO-OPTIMIZATION OF DATA-RATE AND TRACE DIMENSIONS

A technique to optimize the data-rate based on energy per bit is presented in [29] and [30]. However, these studies assume the aggregate bandwidth of the link to be fixed and hence do not put constraints on the total routing width available. As a result, the cross-sectional dimensions of the traces are assumed to be fixed. In this paper, the goal is to co-optimize the data-rate of the link and cross-sectional dimensions of the traces. For a fixed routing width available on a PCB, a BP, or an interposer, the goal is to maximize the aggregate bandwidth, while simultaneously minimizing the energy consumed to transmit one bit over the channel. For example, if the wires are too narrow, the conductor losses in the channel are high, forcing the link to consume more energy and also operate at lower data-rates (per wire). On the other hand, if the wires are too wide, not many wires can fit in the given routing width, thus resulting in a lower aggregate bandwidth. Similarly, operating the link at high data-rates increases the aggregate bandwidth, at the expense of higher energy consumption. This section develops a systematic approach to study the above tradeoff to maximize the aggregate bandwidth per joule of energy supplied to the link.

### A. Key Metrics-Bandwidth Density and Energy per Bit

1) *Bandwidth Density*: It is the aggregate bandwidth of the link per unit routing width. Mathematically, bandwidth density (BWD) can be defined as

$$\text{BWD} = \frac{\text{DR}}{p} \quad (22)$$

where DR is the data-rate and  $p$  is the pitch. This metric highlights the tradeoff between the aggregate bandwidth and available routing width.

2) *Energy per Bit*: It is the total energy required to transmit one bit of information reliably over a channel within a specified BER. Mathematically, energy per bit can be expressed as

$$\text{EPB} = \frac{P_{\text{tot}}}{\text{DR}} \quad (23)$$

where  $P_{\text{tot}}$  is the total power dissipated at the transmitter end to transmit one bit reliably, and DR is the data-rate. The total power includes the dynamic and static power dissipated in the driver, predriver buffers, and equalizers. Since the voltage margin of the signal at the receiver is fixed, the receiver power is assumed to be independent of the channel response; hence, it is not included in the analysis.

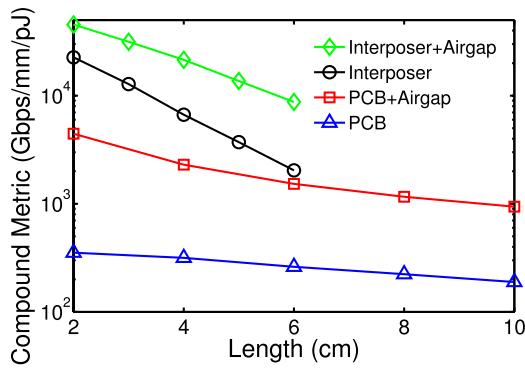

3) *Compound Metric*: BWD and EPB are two independent metrics that give an estimate of system performance and energy, respectively. However, the goal is to co-optimize system performance and energy, rather than focus on system performance or power independently. As a result, a compound metric BWD/EPB, which gives equal importance to both power and performance, is used. For a fixed routing width available on a PCB, the BP, or an interposer, this compound metric gives an estimate of the aggregate bandwidth obtained per joule of energy supplied to the link. In general, a compound metric ( $\text{BWD}^\alpha/\text{EPB}^{2-\alpha}$ ) can be used to give priority to either BWD or energy per bit, based on the application.

### B. Optimization Methodology

A methodology based on co-optimization of performance and energy, similar to that developed in [32], is presented here. As discussed in Section III-A, a compound metric that gives equal importance to both performance and energy (BWD/EPB) is maximized as a function of data-rate and interconnect width. The importance of using the compound metric, as opposed to either BWD or energy per bit, is also discussed in this section.

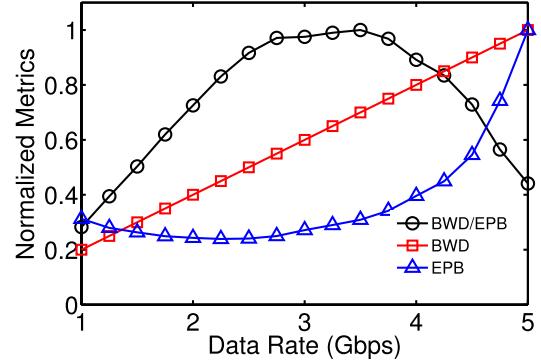

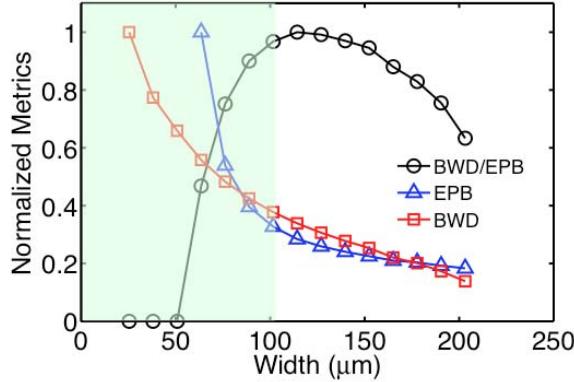

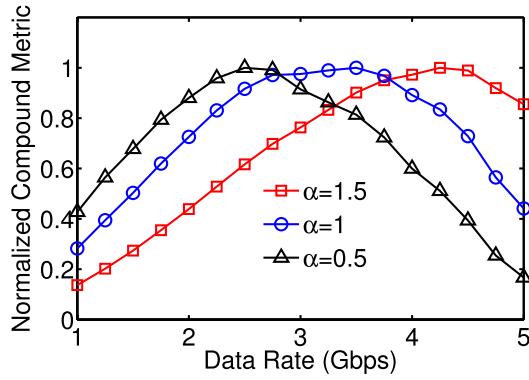

For the purpose of this optimization, the trace width and data-rate per wire are assumed to be independent variables and the circuit limit to the data-rate is assumed to be 50 Gb/s. The metrics, normalized to their maximum value in the range of data-rates, are shown in Fig. 8. For a given trace width, the BWD increases linearly with data-rate. However, energy per bit is not a monotonic function of data-rate. At low data-rates, the minimum current/voltage swing required to transmit a signal reliably over the channel depends more on the noise in the channel, and is almost independent of the

Fig. 8. Normalized metrics—BWD, energy per bit, and compound metric as a function of data-rate for a BP link with a trace width 114.3  $\mu\text{m}$  (optimal width from Fig. 9) and length 100 cm.

loss in the channel. As a result, the total power is almost independent of data-rate; hence, the energy per bit is very high at low data-rates in accordance with (23). However, the channel losses increase with data-rate, and beyond a certain data-rate defined by the channel bandwidth, the voltage swing requirement increases rapidly with data-rate. This gives rise to an interesting bathtub-curve dependence of energy per bit on data-rate, similar to the experimental results shown in [1]. The flat region of the bathtub-curve implies that the data-rate can be increased for a small penalty in energy per bit, up to the point where the energy per bit becomes prohibitively large. Mathematically, this optimal data-rate can be chosen by maximizing the compound metric BWD/EPB, as shown in Fig. 8. Thus, by maximizing the compound metric, we can get a significant increase in data-rate for a small penalty in energy per bit.

For the BP and PCB trace-width optimizations, the spacing is varied as a function of the width to keep the differential impedance constant at 100  $\Omega$ . However, since links on a SI do not necessarily use a matched termination [14], the spacing is assumed to be two-thirds of the linewidth. The metrics, normalized to their maximum value in the range of trace widths, are shown in Fig. 9. At a fixed data-rate, increase in trace width results in an increase in pitch that leads to a reduction in BWD. However, due to the reduction in conductor loss, energy per bit decreases with an increase in trace width. Since the BWD and EPB decrease at different rates with an increase in trace width, there exists an optimal width that maximizes the compound metric, as shown in Fig. 9. Additionally, conventional PCB and BP traces are further limited by minimum width and spacing of 4 mils (101.6  $\mu\text{m}$ ) [27]. Thus, for conventional PCB and BP traces, optimal widths below 4 mils are rounded off to 4 mils, as shown by the shaded area in Figs. 9 and 11. However, the air-gap interconnects are not limited by this minimum width requirement [25].

The above optimization methodology gave equal importance to both aggregate bandwidth and energy per bit. However, the parameter  $\alpha$  for the compound metric can be varied to give priority to either BWD or energy per bit. If  $\alpha > 1$ , a higher priority is given to BWD, thus resulting in a higher optimal data-rate and lower optimal width, as shown in Figs. 10 and 11,

Fig. 9. Normalized metrics—BWD, energy per bit, and compound metric as a function of trace width at a data-rate of 3.5 Gb/s (optimal data-rate from Fig. 8), for a BP link with a trace length of 100 cm. Green area: widths that cannot be achieved with conventional PCB fabrication.

Fig. 10. Normalized compound metric  $BWD^\alpha/EPB^{2-\alpha}$  as a function of data-rate for different values of parameter  $\alpha$ , which decides the relative importance of BWD and energy per bit for the system. The length of the BP trace is 100 cm.

respectively. Similarly, if  $\alpha < 1$ , a higher priority is given to energy per bit, thus resulting in a lower optimal data-rate and a higher optimal width, as shown in Figs. 10 and 11, respectively.

#### IV. PERFORMANCE AND ENERGY BENCHMARKING OF AIR-GAP INTERCONNECTS

In this section, the frequency and time domain models developed in Section II, and the optimization methodology developed in Section III are applied to study the impact of using air-gap interconnects for BP, PCB, and interposer applications. For each trace length, the simulations are run to compute a 2-D matrix of the compound metric  $BWD/EPB$  as a function of trace widths and data-rates; the trace width and data-rate that maximize  $BWD/EPB$  are chosen as the optimal values. As a result of using analytical models for the RLG parameters of transmission lines in the system, the simulations are very fast compared with extraction using Raphael followed by HSPICE simulations; hence, it is possible to run the numerous simulations necessary to explore the entire 2-D design space.

Fig. 11. Normalized compound metric  $BWD^\alpha/EPB^{2-\alpha}$  as a function of trace width for different values of parameter  $\alpha$ , which decides the relative importance of BWD and energy per bit for the system. The length of the BP trace is 100 cm. Green area: widths that cannot be achieved with conventional PCB fabrication.

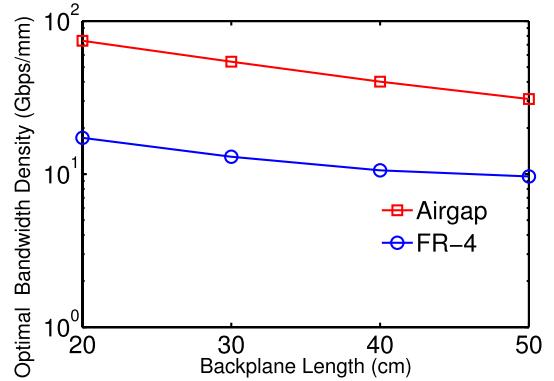

Fig. 12. Optimal BWD of a BP link with conventional FR-4 BP and air-gap BP.

#### A. Airgap Interconnects for BPs

The focus of this section is on the improvement obtained by using air-gap interconnects for BP links. The BP link consists of multiple components discussed in Section II-A. The PCB/BP dielectric material is FR-4, with a dielectric constant of 4.4 and a loss tangent of 0.02. The optimal BWD as a function of trace length for FR-4 and air-gap interconnects is shown in Fig. 12. The optimal BWD of airgap interconnects is roughly 3×–4× better compared with that of FR-4 interconnects. This is because the air-gap technology has larger optimal data-rate, as shown in Fig. 13, and a smaller dielectric height, which requires a smaller width for 100-Ω differential impedance. The optimal width for air-gap interconnects is ~40 μm, whereas the optimal width for FR-4 BPs is the minimum width of 101.6 μm.

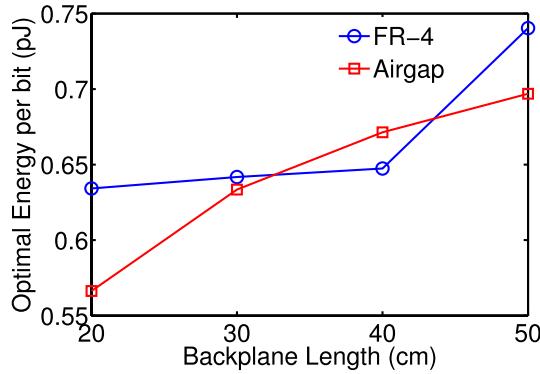

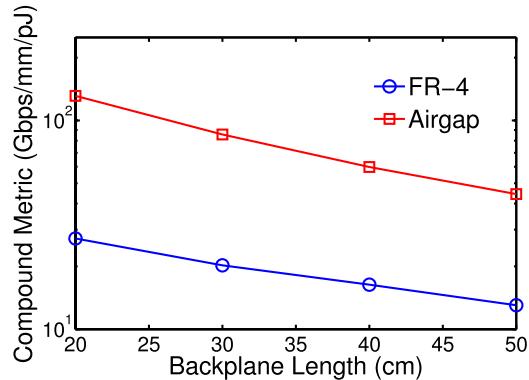

As shown in Fig. 14, the energy per bit for air-gap interconnects is comparable with that of FR-4 interconnects on BPs. This is because, the reduction in dielectric loss is nullified by the increase in conductor loss due to smaller width. Although air-gap interconnects on BPs do not offer any improvement in energy per bit, they offer an improvement in the compound metric (BWD/EPB), as shown in Fig. 15. Additionally, since the compound metric is the one being optimized, it shows

Fig. 13. Optimal data-rate of a BP link with conventional FR-4 BP and air-gap BP.

Fig. 14. Optimal energy per bit of a BP link with conventional FR-4 BP and air-gap BP.

Fig. 15. Optimal compound metric (ratio of BWD and energy per bit) of a BP link with conventional FR-4 BP and air-gap BP.

a monotonic decrease with an increase in the interconnect length.

#### B. Air-Gap Interconnects for PCBs and Interposers

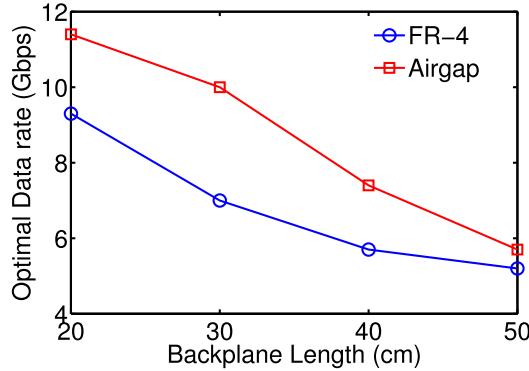

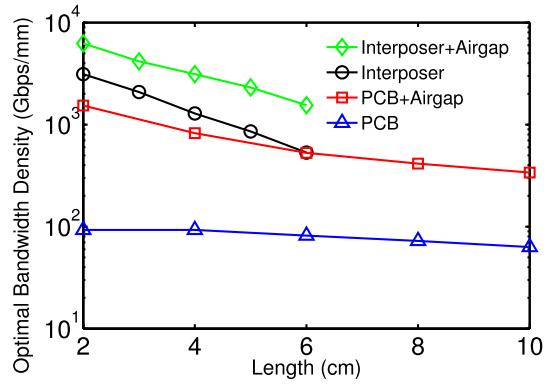

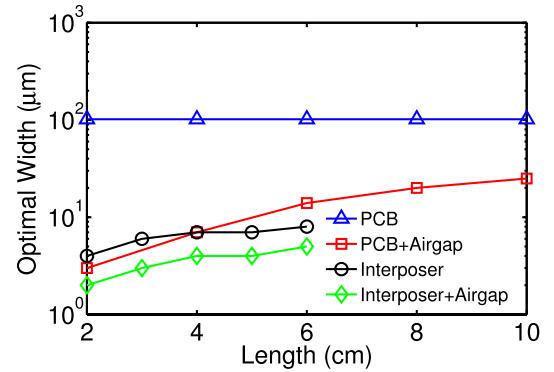

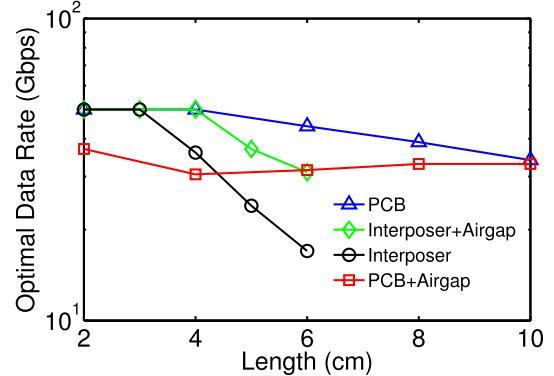

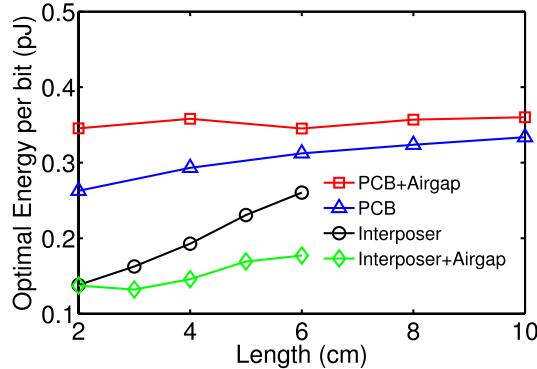

The focus of this section is on the improvement obtained by using air-gap interconnects for PCB and SI links. As shown in Fig. 16, for the PCB link, the BWD of air-gap interconnects is 5×–9× better compared with that of interconnects on FR-4. Although the optimal data-rate of air-gap interconnects is smaller, as shown in Fig. 18, the much smaller optimal width (shown in Fig. 17) of the air-gap interconnects gives rise to

Fig. 16. Optimal BWD of a PCB/interposer link with lossy dielectrics and air-gap dielectrics.

Fig. 17. Optimal trace width of a PCB/interposer link with lossy dielectrics and air-gap dielectrics.

Fig. 18. Optimal data-rate of a PCB/interposer link with lossy dielectrics and air-gap dielectrics.

a better BWD. However, the smaller optimal width of air-gap interconnects results in a 20% higher energy per bit, as shown in Fig. 19.

It is interesting to note that, for BP and PCB links, the improvement of air-gap interconnects degrades with an increase in the trace length. This is because, shorter wires have a higher optimal data-rate and dielectric losses are more dominant at higher data-rates. As the trace lengths increase, the optimal data-rates decrease; hence, the improvement obtained by replacing a lossy dielectric with an air-gap dielectric keeps diminishing. For SI links, the improvement of

Fig. 19. Optimal energy per bit of a PCB/interposer link with lossy dielectrics and air-gap dielectrics.

Fig. 20. Optimal compound metric (ratio of bandwidth density and energy per bit) of a PCB/interposer link with lossy dielectrics and air-gap dielectrics.

air-gap interconnects is  $2 \times$ – $3 \times$  in terms of bandwidth density, and  $1 \times$ – $1.5 \times$  in terms of energy per bit. However, since the interposer traces are not constrained to a differential impedance of  $100 \Omega$ , the improvement of air-gap interconnects in SI links is mainly due to lower capacitance. As a result, the improvement of air-gap interconnects increases with an increase in trace length. The optimal compound metrics for the PCB and SI links are shown in Fig. 20. Since the compound metric is the one being optimized, unlike other optimal metrics, it shows a monotonic decrease with interconnect length.

## V. DISCUSSION OF FABRICATION PROCESSES AND CHALLENGES

The air-gap interconnect in this paper is a heterogeneous structure with differential striplines supported on a polymer membrane, where the regions between the polymer membrane and top and bottom ground planes are essentially air gaps [Fig. 2(b)]. This section gives a brief explanation about the processes involved in developing these air-gap structures and the important challenges associated with their fabrication.

### A. Fabrication Process

The air-gap creation mechanism is based on the thermal decomposition of a sacrificial polymer and the diffusion of its decomposed products through a polymer membrane, thus leaving a gaseous void in place. The general processing

steps of the proposed air-gap interconnect fabrication can be summarized as follows:

- 1) electroplating of the bottom ground plane;

- 2) patterning of polymer columns to create trenches for the bottom air-gap region;

- 3) inlay of a sacrificial polymer inside the trenches between polymer columns, i.e., bottom air-gap region;

- 4) coating of the polymer membrane;

- 5) electroplating of striplines on top of the polymer membrane;

- 6) patterning of another layer of polymer columns for definition of the top air-gap region;

- 7) inlay of sacrificial polymer inside the top air-gap region;

- 8) patterning of the top polymer overcoat;

- 9) simultaneous decomposition of the sacrificial polymer both in top and bottom air-gap regions, and curing of the polymer membrane and columns;

- 10) electroplating of the top ground plane.

The sacrificial polymer acts as a temporary space holder during other processing steps, and thermally decomposes to create air gaps. PPC was previously demonstrated to be a promising sacrificial polymer in air-gap transmission line fabrication on PCB substrates [44]. Air-gap structures for microelectromechanical systems packaging have been fabricated using PPC with a hybrid organic-inorganic polyhedral epoxycyclohexyl oligomeric silsesquioxanes overcoat on silicon substrates [45]. PPC thermally decomposes by photoacid catalysis in a narrow and useful temperature window completely into volatile products, which diffuse through the polymer membranes [46]. The mechanical support for striplines in Fig. 2(b) is provided by the polymer membrane, which extends to top of the polymer columns on either side of air gaps. The same solvent-cast material can be used for both the membrane and the columns, e.g., polyimide, avatrel, SU-8, and cyclotene [47].

### B. Fabrication Challenges

For fabrication of air-gap structures on PCB and SI, any combination of PPC and structural polymer can be used. One important issue is the material compatibility of PPC with structural polymer, i.e., otherwise distortion of patterns by partial dissolution of polymers due to solvent transfer from one to another. In [47], it was shown that a thin layer of plasma-enhanced chemical vapor deposition-deposited  $\text{SiO}_2$  (as small as  $530 \text{ \AA}$ ) on top of polycarbonate-based sacrificial polymers is successful in preventing solvent transfer between polymers without deformation of original air-gap region. However, the Coefficient of Thermal Expansion mismatch between polymers ( $\sim 30$ – $50 \text{ ppm/K}$ ) and  $\text{SiO}_2$  ( $\sim 0.5 \text{ ppm/K}$ ) should be considered in selecting the processing temperatures, since cracking might be observed in  $\text{SiO}_2$  layer at high temperatures. Recently, PPC-cyclotene combination has been identified to be a fully compatible sacrificial polymer-structural polymer pair not requiring any solvent barrier layer [25]. The choice of structural polymer should be considered early in the photomask design phase, since the mechanical stability of the polymer membrane is dependent on the width of the air-gap

region, i.e., the wider the air-gap region, the more vulnerable the mechanical stability of polymer membrane, and there is a higher chance of sagging of the polymer membrane after air-gap creation [25], [45]. PPC can be thermally planarized by partial decomposition of upper layers of PPC in the air-gap region. In this case, the photomask for patterning sacrificial polymer can be widened in order to compensate for lateral photoacid diffusion into the airgap region, which can deform the air-gap pattern [25]. Any nonuniformity in the air-gap region can result in deviations in the final electrical performance of air-gap interconnect. A possible use of  $\text{SiO}_2$  barrier layer increases the heterogeneity of the air gaps, which directly affects the dielectric loss.

## VI. CONCLUSION

Frequency and time domain models for BP, PCB, and SI are developed here and validated using HSPICE. The models take into account ISI noise, NEXT, and FEXT, and provide a platform for the comparison of air-gap interconnects against conventional interconnects on FR-4 and SI interconnects on silicon dioxide. For BP links, the air-gap interconnects show an improvement of  $3\times$ – $4\times$  in aggregate bandwidth at a comparable energy per bit. Similarly, for PCB links, the air-gap interconnects provide a  $5\times$ – $9\times$  improvement in aggregate bandwidth at the expense of a 20% higher energy per bit. An improvement of  $2\times$ – $3\times$  in aggregate bandwidth and an improvement of  $1\times$ – $1.5\times$  in energy per bit is achieved for air-gap interconnects on a SI. For both PCB and BP links, the traces are designed for a  $100\text{-}\Omega$  differential impedance; hence, the improvement in BWD of air-gap interconnects is mainly from the reduced dielectric losses. Since the optimal data-rates are higher at smaller lengths, and the dielectric losses are more severe at higher data-rates, for PCB and BP links, the improvement in BWD of air-gap interconnects decreases with an increase in length. However, since the SI traces are not constrained to have a differential impedance of  $100\text{ }\Omega$ , their improvement mainly comes from the smaller capacitance. As a result, for the SI link, the improvement of air-gap interconnects increases with an increase in trace length.

## ACKNOWLEDGMENT

The authors would like to thank Y.-C. Chen, R. Saha, A. Pandey, A. Kapoor, and J. Chen for the insightful discussions and all their help and support for this paper.

## REFERENCES

- [1] G. Balamurugan *et al.*, "A scalable 5–15 Gbps, 14–75 mW low-power I/O transceiver in 65 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 43, no. 4, pp. 1010–1019, Apr. 2008.

- [2] F. O'Mahony *et al.*, "A  $47\times 10$  Gb/s 1.4 mW/Gb/s parallel interface in 45 nm CMOS," *IEEE J. Solid-State Circuits*, vol. 45, no. 12, pp. 2828–2837, Dec. 2010.

- [3] H. Cho, P. Kapur, and K. Saraswat, "Power comparison between high-speed electrical and optical interconnects for interchip communication," *J. Lightw. Technol.*, vol. 22, no. 9, pp. 2021–2033, Sept. 2004.

- [4] W. J. Dally and J. W. Poulton, *Digital Systems Engineering*. Cambridge, U.K.: Cambridge Univ. Press, 1998.

- [5] Y. Li, J. Al, and J. Popelik, "Board-level 2-D data-capable optical interconnection circuits using polymer fiber-image guides," *Proc. IEEE*, vol. 88, no. 6, pp. 794–805, Jun. 2000.

- [6] R. Chen *et al.*, "Fully embedded board-level guided-wave optoelectronic interconnects," *Proc. IEEE*, vol. 88, no. 6, pp. 780–793, Jun. 2000.

- [7] D. Miller, "Rationale and challenges for optical interconnects to electronic chips," *Proc. IEEE*, vol. 88, no. 6, pp. 728–749, Jun. 2000.

- [8] S. W. Yoon, D. W. Yang, J. H. Koo, M. Padmanathan, and F. Carson, "3D TSV processes and its assembly/packaging technology," in *Proc. IEEE Int. Conf. 3D Syst. Integr.*, Sept. 2009, pp. 1–5.

- [9] E. Beyne *et al.*, "Through-silicon via and die stacking technologies for microsystems-integration," in *Proc. IEEE IEDM*, Dec. 2008, pp. 1–4.

- [10] J. Kim *et al.*, "High-frequency scalable electrical model and analysis of a through silicon via (TSV)," *IEEE Trans. Compon. Packag. Manuf. Technol.*, vol. 1, no. 2, pp. 181–195, Feb. 2011.

- [11] M. Matsuo, N. Hayasaka, K. Okumura, E. Hosomi, and C. Takubo, "Silicon interposer technology for high-density package," in *Proc. 50th Electron. Compon. Technol. Conf.*, 2000, pp. 1455–1459.

- [12] N. Kim, D. Wu, D. Kim, A. Rahman, and P. Wu, "Interposer design optimization for high frequency signal transmission in passive and active interposer using through silicon via (TSV)," in *Proc. IEEE 61st ECTC*, Jun. 2011, pp. 1160–1167.

- [13] K. Zoschke *et al.*, "TSV based silicon interposer technology for wafer level fabrication of 3D SiP modules," in *Proc. IEEE ECTC*, Jun. 2011, pp. 836–843.

- [14] T. Dickson *et al.*, "An  $8\times 10$ -Gb/S source-synchronous I/O system based on high-density silicon carrier interconnects," *IEEE J. Solid-State Circuits*, vol. 47, no. 4, pp. 884–896, Apr. 2012.

- [15] T. Spencer, P. Joseph, T. H. Kim, M. Swaminathan, and P. Kohl, "Air-gap transmission lines on organic substrates for low-loss interconnects," *IEEE Trans. Microw. Theory Technol.*, vol. 55, no. 9, pp. 1919–1925, Sept. 2007.

- [16] J. Noguchi *et al.*, "Simple self-aligned air-gap interconnect process with cu/fsg structure," in *Proc. IEEE Int. Interconnect Technol. Conf.*, Jun. 2003, pp. 68–70.

- [17] N. Nakamura, N. Matsunaga, T. Kaminatsui, K. Watanabe, and H. Shibata, "Cost-effective air-gap interconnects by all-in-one post-removing process," in *Proc. IITC*, Jun. 2008, pp. 193–195.

- [18] X. Zhang, S.-K. Ryu, R. Huang, P. S. Ho, J. Liu, and D. Toma, "Impact of process induced stresses and chip-packaging interaction on reliability of air-gap interconnects," in *Proc. IITC*, Jun. 2008, pp. 135–137.

- [19] B. Shieh *et al.*, "Electromigration reliability of low capacitance air-gap interconnect structures," in *Proc. IEEE Int. Interconnect Technol. Conf.*, Jun. 2002, pp. 203–205.

- [20] V. Sukharev, B. Shieh, R. Choudhury, C. Park, and K. Saraswat, "Reliability studies on multilevel interconnection with intermetal dielectric air gaps," *Microelectron. Rel.*, vol. 41, no. 9, p. 1631–1635, 2001.

- [21] B. Shieh *et al.*, "Integration and reliability issues for low capacitance air-gap interconnect structures," in *Proc. IEEE Int. Interconnect Technol. Conf.*, Jun. 1998, pp. 125–127.

- [22] S. Park, S. A. Bidstrup, and P. A. Kohl, "Air-gaps for high performance on-chip interconnect part I: Improvement in thermally decomposable template," *J. Electron. Mater.*, vol. 37, no. 10, pp. 1524–1533, 2008.

- [23] B. Shieh *et al.*, "Air-gap formation during IMD deposition to lower interconnect capacitance," *IEEE Electron Device Lett.*, vol. 19, no. 1, pp. 16–18, Jan. 1998.

- [24] J. Kash *et al.*, "Optical interconnects in exascale supercomputers," in *Proc. 23rd Annu. Meeting IEEE Photon. Soc.*, Nov. 2010, pp. 483–484.

- [25] R. Sharma *et al.*, "Design and fabrication of low-loss horizontal and vertical interconnect links using air-clad transmission lines and through silicon vias," in *Proc. IEEE 62nd ECTC*, Jun. 2012, pp. 2005–2012.

- [26] E. Uzunlar *et al.*, "Design and fabrication of ultra low-loss, high-performance 3D chip-chip air-clad interconnect pathway," in *Proc. IEEE 63rd ECTC*, May 2013, pp. 1425–1432.

- [27] B. Olney. (2011, Nov.). *The Perfect Stackup (for High-Speed Design)*. The PCB Magazine [Online]. Available: [http://www.icd.com.au/articles/Perfect\\_Stackup\\_PCB-Nov2011.pdf](http://www.icd.com.au/articles/Perfect_Stackup_PCB-Nov2011.pdf)

- [28] Synopsys Inc., Mountain View, CA, USA. (2008). *HSPICE* [Online]. Available: <http://www.synopsys.com/Tools/Verification/AMSVerification/CircuitSimulation/HSPICE/Pages/default.aspx>

- [29] H. Hatamkhani and C.-K. Yang, "A study of the optimal data rate for minimum power of I/Os," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 53, no. 11, pp. 1230–1234, Nov. 2006.

- [30] K.-L. Wong, H. Hatamkhani, M. Mansuri, and C.-K. Yang, "A 27-mW 3.6-Gb/s I/O transceiver," *IEEE J. Solid-State Circuits*, vol. 39, no. 4, pp. 602–612, Apr. 2004.

- [31] K. J. Han, X. Gu, Y. Kwark, L. Shan, and M. Ritter, "Modeling on-board via stubs and traces in high-speed channels for achieving higher data bandwidth," *IEEE Trans. Compon. Packag. Manuf. Technol.*, vol. 4, no. 2, pp. 268–278, Feb. 2014.

- [32] V. Kumar, R. Bashirullah, and A. Naeemi, "Modeling, optimization and benchmarking of chip-to-chip electrical interconnects with low loss air-clad dielectrics," in *Proc. IEEE 61st ECTC*, Jun. 2011, pp. 2084–2090.

- [33] C. R. Paul, *Analysis of Multiconductor Transmission Lines*. New York, NY, USA: Wiley, 2008.

- [34] B. Kim, Y. Liu, T. Dickson, J. Bulzacchelli, and D. Friedman, "A 10-Gb/s compact low-power serial I/O with DFE-IIR equalization in 65-nm CMOS," *IEEE J. Solid-State Circuits*, vol. 44, no. 12, pp. 3526–3538, Dec. 2009.

- [35] Synopsys Inc., Mountain Valley, CA, USA. (1996). *RAPHAEL* [Online]. Available: <http://www.synopsys.com/TOOLS/TCAD/INTERCONNECTSIMULATION/Pages/Raphael.aspx>

- [36] H. W. Johnson *et al.*, *High-Speed Digital Design: A Handbook of Black Magic*, vol. 1. Englewood Cliffs, NJ, USA: Prentice-Hall, 1993.

- [37] E. Chan, H. Chen, and C. Y. Chung, "High speed DDR performance in 4 vs 6 layer FCBGA package design," in *Proc. 54th Electron. Compon. Technol. Conf.*, vol. 1, 2004, pp. 314–319.

- [38] W. Zhao, X. Li, S. Gu, S. Kang, M. Nowak, and Y. Cao, "Field-based capacitance modeling for sub-65-nm on-chip interconnect," *IEEE Trans. Electron Devices*, vol. 56, no. 9, pp. 1862–1872, Sept. 2009.

- [39] V. Kumar, L. Zheng, M. Bakir, and A. Naeemi, "Compact modeling and optimization of fine-pitch interconnects for silicon interposers," in *Proc. IEEE ITC*, Jun. 2013, pp. 1–3.

- [40] T. Liang, S. Hall, H. Heck, and G. Brist, "A practical method for modeling PCB transmission lines with conductor surface roughness and wideband dielectric properties," in *IEEE MTT-S Int. Microw. Symp. Dig.*, Jun. 2006, pp. 1780–1783.

- [41] T. Arabi, A. Murphy, T. Sarkar, R. Harrington, and A. Djordjevic, "On the modeling of conductor and substrate losses in multiconductor, multidielectric transmission line systems," *IEEE Trans. Microw. Theory Techn.*, vol. 39, no. 7, pp. 1090–1097, Jul. 1991.

- [42] A. R. Djordjevic, R. Biljje, V. Likar-Smiljanic, and T. Sarkar, "Wideband frequency-domain characterization of FR-4 and time-domain causality," *IEEE Trans. Electromagn. Compat.*, vol. 43, no. 4, pp. 662–667, Nov. 2001.

- [43] (2008, Sep.). *ASU Predictive Technology Models* [Online]. Available: <http://ptm.asu.edu/latest.html>

- [44] J. Chen, Y. Hu, Y.-C. Chen, R. Saha, R. Bashirullah, and P. Kohl, "Air cavity low-loss transmission lines for high speed serial link applications," in *Proc. IEEE 61st ECTC*, Jun. 2011, pp. 2146–2151.

- [45] R. Saha, N. Fritz, S. A. Bidstrup-Allen, and P. A. Kohl, "Packaging-compatible wafer level capping of MEMS devices," *Microelectron. Eng.*, vol. 104, pp. 75–84, Apr. 2013.

- [46] T. J. Spencer, Y.-C. Chen, R. Saha, and P. A. Kohl, "Stabilization of the thermal decomposition of poly (propylene carbonate) through copper ion incorporation and use in self-patterning," *J. Electron. Mater.*, vol. 40, no. 6, pp. 1350–1363, 2011.

- [47] P. J. Joseph, H. A. Kelleher, S. A. B. Allen, and P. A. Kohl, "Improved fabrication of micro air-channels by incorporation of a structural barrier," *J. Micromech. Microeng.*, vol. 15, no. 1, p. 35, 2005.

**Vachan Kumar** (S'10) received the B.E. degree in electronics and communication engineering from the National Institute of Technology Karnataka, Surathkal, India, in 2006. He is currently pursuing the Ph.D. degree in electrical and computer engineering with the Nanoelectronics Research Laboratory, Georgia Institute of Technology, Atlanta, GA, USA.

He was with Advanced Micro Devices, Inc., Bangalore, India, as a Design Engineer, where he was designing several critical blocks used in 45 and 32-nm microprocessor cores. In 2013, he was an SRCEA Intern Scholar at GlobalFoundries, Malta, NY, USA, where he was involved in power/performance analysis of 3-D ICs. His current research interests include modeling and benchmarking emerging interconnect technologies for both on-chip and off-chip applications.

**Rohit Sharma** (M'07) received the B.Eng. degree in electronics and telecommunication engineering from North Maharashtra University, Jalgaon, India, in 2000, the M.Tech. degree in engineering systems from the Dayalbagh Educational Institute, Agra, India, in 2003, and the Ph.D. degree in electronics and communication engineering from the Jaypee University of Information Technology, Solan, India, in 2009.

He was a Brain Korea Post-Doctoral Fellow at the Design Automation Laboratory, Seoul National University, Seoul, Korea, in 2010. From 2011 to 2012, he was an Indo-U.S. Research Fellow at the Interconnect Focus Center, Georgia Institute of Technology, Atlanta, GA, USA. Since 2012, he has been with the Faculty of Electrical Engineering at the Indian Institute of Technology Ropar, Rupnagar, India. His current research interests include the design and optimization of ultralow-loss air-clad interconnects, 3-D interconnects, and carbon-based nanoelectronic design.

**Erdal Uzunlar** (S'13) was born in Tekirdag, Turkey, in 1984. He received the B.S. degree in chemical engineering from Bogazici University, Istanbul, Turkey, in 2008, and the M.S. degree in chemical and biological engineering from Koc University, Istanbul, in 2010. He is currently pursuing the Ph.D. degree in chemical and biomolecular engineering with the Georgia Institute of Technology, Atlanta, GA, USA.

His research focuses mainly on material and processing technologies in microelectronics. His current research interests include low-loss airgap chip-to-chip interconnection, low-cost MEMS packaging using sacrificial polymer-based airgaps, inexpensive novel catalysts for electroless copper deposition on nonconductive surfaces, and thermal, physical, and chemical characterization of sacrificial polymers.

**Li Zheng** received the B.S. degree from Zhejiang University, Hangzhou, China, in 2006, and the dual M.S. degree in electrical and computer engineering from Shanghai Jiao Tong University, Shanghai, China, and the Georgia Institute of Technology, Atlanta, GA, USA, in 2009, where he is currently pursuing the Ph.D. degree in electrical and computer engineering.

His current research interests include embedded microfluidic cooling, power delivery modeling and chip-to-chip signaling modeling for high-performance silicon interposer, and 3-D integrated systems.

**Rizwan Bashirullah** (S'98–M'04) received the B.S. degree in electrical engineering from the University of Central Florida, Orlando, FL, USA, and the M.S. and Ph.D. degrees in electrical engineering from North Carolina State University, Raleigh, NC, USA, in 1999 and 2004, respectively.

He joined the Department of Electrical and Computer Engineering at the University of Florida, Gainesville, FL, USA, in 2004, where he is currently a Tenured Associate Professor. He has authored and co-authored about 100 referred technical abstracts and papers in conferences and journals. His current research interests include mixed-signal circuits for biomedical applications, power delivery systems, and on-chip/off-chip signaling subsystems.

Dr. Bashirullah served as an Associate Editor of the *IEEE TRANSACTIONS ON BIOMEDICAL ENGINEERING* from 2005 to 2009, and as a Guest Editor of the *IEEE ANTENNA PROPAGATION LETTERS* and the *IEEE MICROWAVE MAGAZINE*. He has also served as the Conference Organizing Chair for Biomedical Wireless in various organizing positions for the IEEE Radio Wireless Week and as a Technical Program Committee Member for the International Symposium on Quality Electronic Design, the International Symposium on Low Power Electronics and Design, the IEEE International Symposium on Circuits and Systems, the IEEE Radio and Wireless Symposium, the IEEE Microwave Theory and Techniques Society (MTT-S), and the Biomedical Circuits and Systems Conference. He was a recipient of the 2005 National Science Foundation's Early Career Development Award, the 2010 University of Florida Inventor Recognition Award, and the 2011 *Microwave Magazine* Best Paper Award of the IEEE MTT-S.

**Paul Kohl** (A'92–M'03) received the Ph.D. degree in chemistry from the University of Texas at Austin, Austin, TX, USA, in 1978.

He was with AT&T Bell Laboratories, Murray Hill, NJ, USA, from 1978 to 1989. During that time, he was involved in new chemical processes for silicon and compound semiconductor devices and their packaging. In 1989, he joined the faculty of the School of Chemical and Biomolecular Engineering, Georgia Institute of Technology (Georgia Tech), Atlanta, GA, USA, where he is currently a Regents'

Professor and the Hercules Inc./Thomas L. Gossage Chair. He is involved in the synthesis of ionic conducting polymers for electrochemical devices and high-energy density batteries. He has 250 journal publications and more than 400 conference presentations, and holds 57 U.S. patents. His current research interests include new processes and materials for the interconnect and packaging of integrated circuits and MEMS devices.

Dr. Kohl was an Editor of the *Journal of The Electrochemical Society* and *Electrochemical and Solid-State Letter*, the Director of the MARCO Interconnect Focus Center, Georgia Tech, and was the President of the Electrochemical Society.

**Azad Naeemi** (S'99–M'04–SM'04) received the B.S. degree in electrical engineering from Sharif University, Tehran, Iran, in 1994, and the M.S. and Ph.D. degrees in electrical and computer engineering from the Georgia Institute of Technology (Georgia Tech), Atlanta, GA, USA, in 2001 and 2003, respectively.

He was a Research Engineer with the Microelectronics Research Center, Georgia Tech, from 2003 to 2008, where he joined the School of Electrical and Computer Engineering faculty, and is currently an Associate Professor. His current research interests include exploring nanotechnology solutions to the challenges facing giga and terascale systems.

Dr. Naeemi was a recipient of the IEEE Electron Devices Society's Paul Rappaport Award for the best paper that has appeared in the IEEE TRANSACTIONS ON ELECTRON DEVICES in 2007. He was also a recipient of an NSF CAREER Award, an SRC Inventor Recognition Award, and three Best Paper Awards at international conferences.

**Muhammed S. Bakir** (SM'12) received the B.E.E. (*summa cum laude*) degree from Auburn University, Auburn, AL, USA, in 1999, and the M.S. and Ph.D. degrees in electrical and computer engineering from the Georgia Institute of Technology (Georgia Tech), Atlanta, GA, USA, in 2000 and 2003, respectively.

He is currently an Associate Professor and the ON Semiconductor Junior Professor with the School of Electrical and Computer Engineering at Georgia Tech.

Dr. Bakir is an Editor of the IEEE TRANSACTIONS ON ELECTRON DEVICES, an Associate Editor of the IEEE TRANSACTIONS ON COMPONENTS, PACKAGING AND MANUFACTURING TECHNOLOGY, and was a Guest Editor of the June 2011 special issue of the IEEE Journal of Selected Topics in Quantum Electronics. He is also a member of the International Technology Roadmap for Semiconductor's technical working group for assembly and packaging. He was a recipient of the 2013 Intel Early Career Faculty Honor Award, the 2012 DARPA Young Faculty Award, the 2011 IEEE CPMT Society Outstanding Young Engineer Award, and was an Invited Participant in the 2012 National Academy of Engineering Frontiers of Engineering Symposium. He was also a recipient of the Semiconductor Research Corporation's Inventor Recognition Awards in 2002, 2005, and 2009. He and his research group have received 12 conference and student paper awards, including one from the IEEE Custom Integrated Circuits Conference, five from the IEEE Electronic Components and Technology Conference, and three from the IEEE International Interconnect Technology Conference.